Enabling Watchdog Timers on the Zynq Ultrascale+ MPSoC: Step by Step

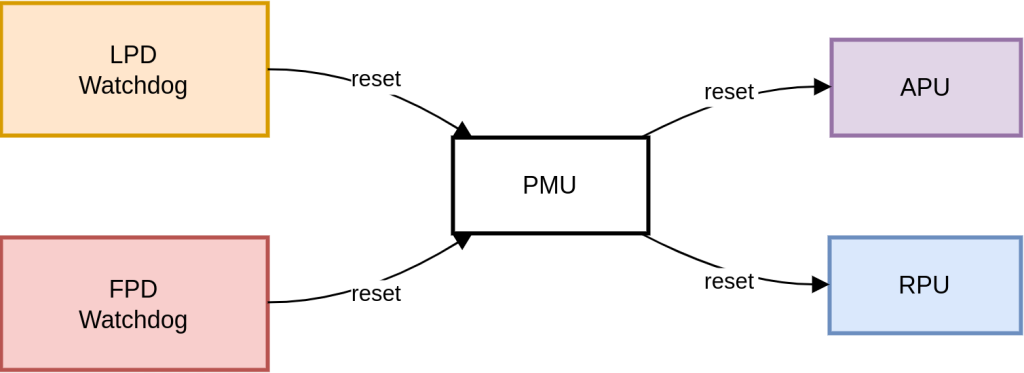

Reading Time: 5 minutes Introduction Today’s Embedded systems have become quite complex, often containing multiple processors and software. As such, the risk of a system locking up becomes more of a concern. To that end, watchdog timer peripherals have become an integral part of these systems. A hardware watchdog timer is a type of timer that, once enabled, requires […]

Enabling Watchdog Timers on the Zynq Ultrascale+ MPSoC: Step by Step Read More »