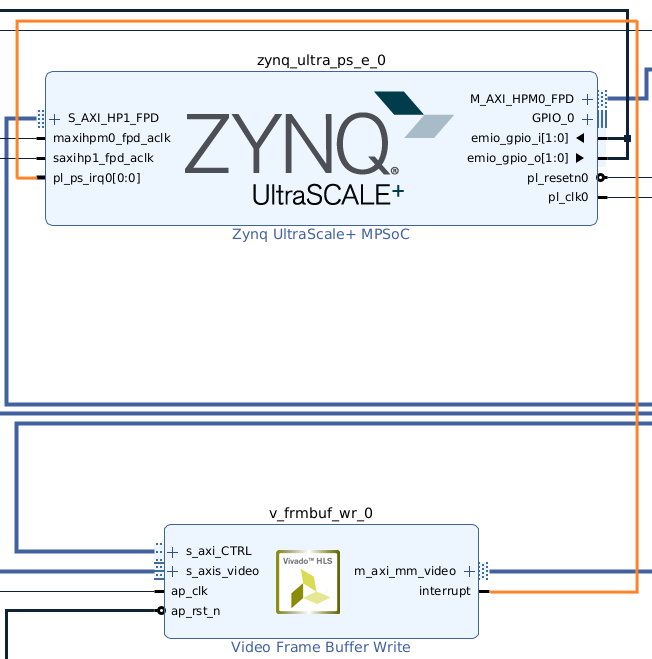

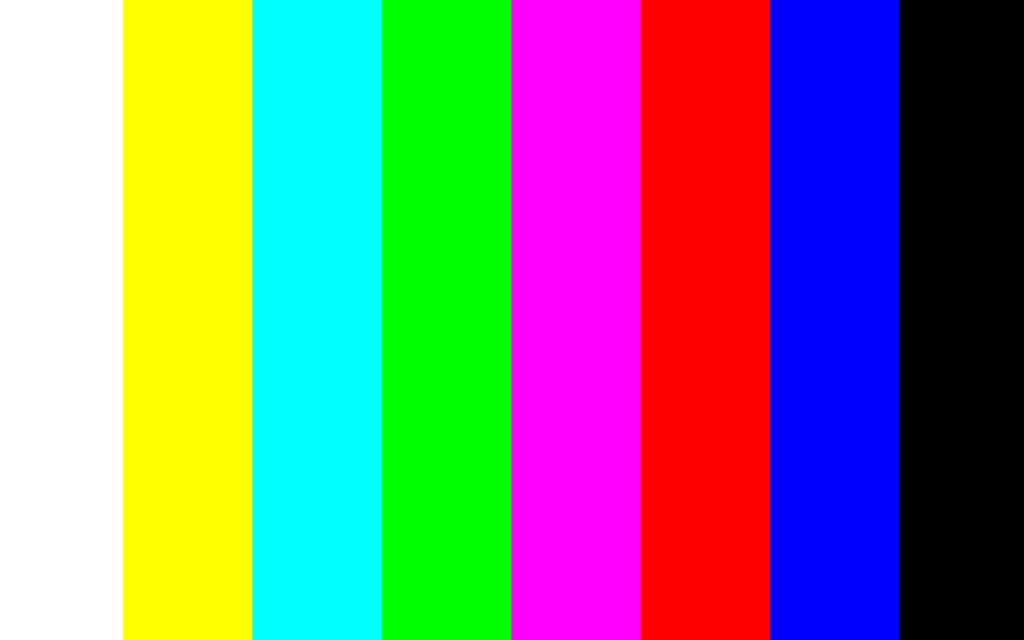

A Visual Reference Guide to the AMD/Xilinx Video Test Pattern Generator (TPG)

Reading Time: 5 minutes At Cornersoft Solutions, a significant portion of our work over the last few years has focused on custom video pipelines using AMD/Xilinx designs. When dealing with video, one of the first recommendations we make to customers is to utilize the AMD/Xilinx Video Test Pattern Generator (TPG). We always recommend building complex video designs iteratively—especially on […]

A Visual Reference Guide to the AMD/Xilinx Video Test Pattern Generator (TPG) Read More »