Yocto Project Expert Tips: The Power of devshell

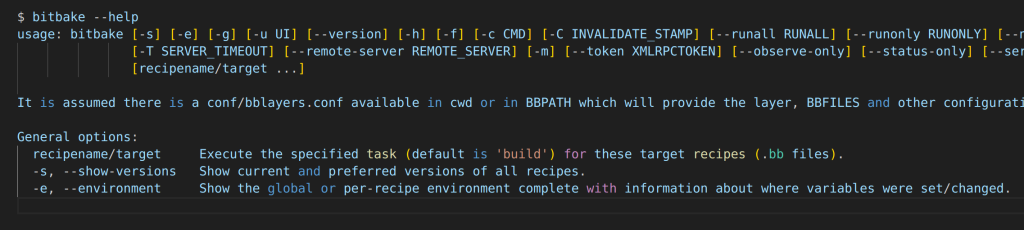

Reading Time: 4 minutes Introduction Building a Yocto project based distribution often means encountering frustrating errors when building recipes. While bitbake logs these failures, deciphering the root cause can be like finding a needle in a haystack. Each recipe and build process is unique, so relying solely on logs can be inefficient and overwhelming. Luckily, the Yocto project provides […]

Yocto Project Expert Tips: The Power of devshell Read More »